設計驗證及積體電路工程

量測需求

在量測積體電路及設計驗證時,工程師面對繁複的測試儀器配置挑戰,例如直流(DC)和 射頻(RF)電源及電子儀表、示波器/向量網路分析儀等等。這些挑戰在考量量測溫度、高阻抗、頻率範圍以及使用高針數探針卡量測積體電路時,更顯困難與複雜;自動測試設備(ATE)的電纜連接介面問題亦不少見。

旺矽解決方案

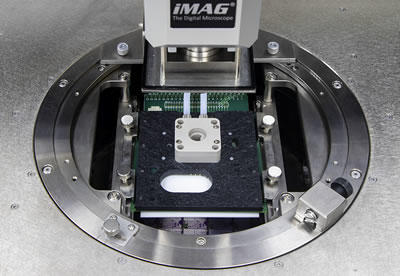

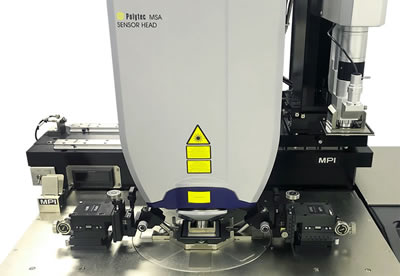

旺矽工程探針台系統具有彈性的設計:支援尺寸大小從 50 至 300 mm 的晶圓,並具備寬廣溫度範圍的直流(DC)、三軸(triaxial)及射頻(RF)載台,可搭配各款初、高階直流(DC)/ 射頻(RF)微定位器(MicroPositioners)、工作距離長的單筒顯微鏡及光學配件等;對任何量測需求及成本預算,旺矽皆能提供您最理想的解決方案。

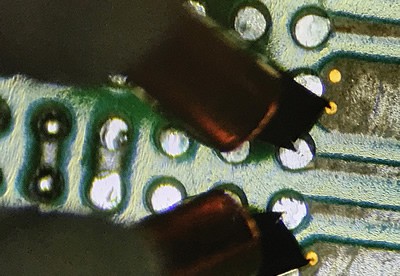

旺矽完善的 RF 探針積體電路解決方案為精準需求高的射頻量測及高頻校正,推出校正軟體 QAlibria® 以及旺矽射頻和微波探針,提供您最完美的量測環境。

TITAN™ RF 探針系列旗下的雙訊號 GSGSG 及 GSSG 探針是量測毫米波差動積體電路的最佳選擇。針對使用示波器之量測,旺矽亦提供具備可更換式葉片及高輸入阻抗的寬頻主動式探針。